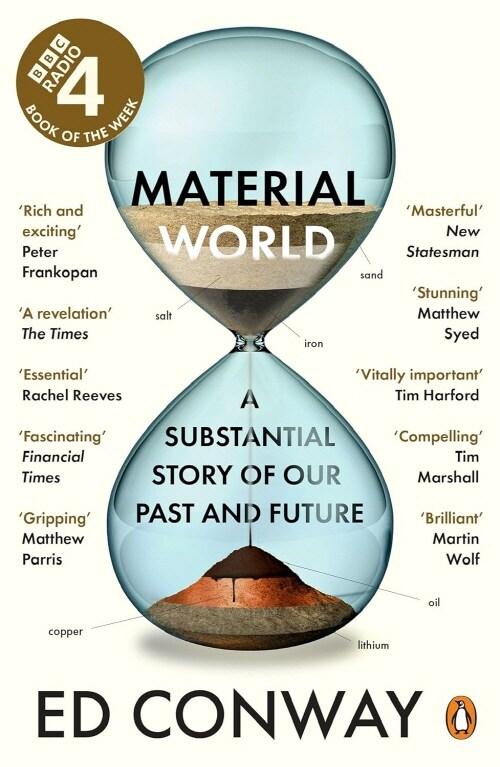

책 이미지

책 정보

· 분류 : 외국도서 > 기술공학 > 기술공학 > 전기공학

· ISBN : 9780387285931

· 쪽수 : 342쪽

· 출판일 : 2006-03-07

목차

Preface. Acronyms. 1. SETS, RELATIONS, AND FUNCTIONS. 1. Sets. 2. Relations. 3. Functions. 4. Representations of Logic Functions. 5. Factored Expressions. 6. Exercises and Problems. 2. ALGEBRAIC STRUCTURES FOR LOGIC DESIGN. 1. Algebraic Structure. 2. Finite Groups. 3. Finite Rings. 4. Finite Fields. 5. Homomorphisms. 6. Matrices. 7. Vector spaces. 8. Algebra. 9. Boolean Algebra. 10. Graphs. 11. Exercises and Problems. 3. FUNCTIONAL EXPRESSIONS FOR SWITCHING FUNCTIONS. 1. Shannon Expansion Rule. 2. Reed-Muller Expansion Rules. 3. Fast Algorithms for Calculation of RM-expressions. 4. Negative Davio Expression. 5. Fixed Polarity Reed-Muller Expressions. 6. Algebraic Structures for Reed-Muller Expressions. 7. Interpretation of Reed-Muller Expressions. 8 Kronecker Expressions. 9. Word-Level Expressions. 10. Walsh Expressions. 11. Walsh Functions and Switching Variables. 12. Walsh Series. 13. Relationships Among Expressions. 14. Generalizations to Multiple-Valued Functions. 15. Exercises and Problems. 4. DECISION DIAGRAMS FOR REPRESENTATION OF SWITCHING FUNCTIONS. 1. Decision Diagrams. 2. Decision Diagrams over Groups. 3. Construction of Decision Diagrams. 4. Shared Decision Diagrams. 5. Multi-terminal binary decision diagrams. 6. Functional Decision Diagrams. 7. Kronecker decision diagrams. 8. Pseudo-Kronecker decision diagrams. 9. Spectral Interpretation of Decision Diagrams. 10. Reduction of Decision Diagrams. 11. Exercises and Problems. 5. CLASSIFICATION OF SWITCHING FUNCTIONS. 1. NPN-classification. 2. SD-Classification. 3. LP-classification. 4. Universal Logic Modules. 5. Exercises and Problems. 6. SYNTHESIS WITH MULTIPLEXERS. 1. Synthesis with Multiplexers. 2. Applications of Multiplexers. 3. Demultiplexers. 4. Synthesis with Demultiplexers. 5. Applications of Demultiplexers. 6. Exercises and Problems. 7. REALIZATIONS WITH ROM. 1. Realizations with ROM. 2. Two-level Addressing in ROM Realizations. 3. Characteristics of Realizations with ROM. 4. Exercises and Problems. 8. REALIZATIONS WITH PROGRAMMABLE LOGIC ARRAYS. 1. Realizations with PLA. 2. The optimization of PLA. 3. Two-level Addressing of PLA. 4. Folding of PLA. 5. Minimization of PLA by Characteristic Functions. 6. Exercises and Problems. 9. UNIVERSAL CELLULAR ARRAYS. 1. Features of Universal Cellular Arrays. 2. Realizations with Universal Cellular Arrays. 3. Synthesis with Macro Cells. 4. Exercises and Problems. 10. FIELD PROGRAMMABLE LOGIC ARRAYS. 1. Synthesis with FPGAs. 2. Synthesis with Antifuse-Based FPGAs. 3. Synthesis with LUT-FPGAs. 4. Exercises and Problems. 11. BOOLEAN DIFFERENCE AND APPLICATIONS IN TESTING LOGIC NETWORKS. 1. Boolean Difference. 2. Properties of the Boolean Difference. 3. Calculation of the Boolean Difference. 4. Boolean Difference in Testing Logic Networks. 5. Easily Testable Logic Networks. 6. Easily Testable Realizations from PPRM-expressions. 7. Easily Testable Realizations from GRM-expressions. 8. Exercises and Problems. 12. SEQUENTIAL NETWORKS. 1. Basic Sequential Machines. 2. State Tables. 3. Conversion of Sequential Machines. 4. Minimization of States. 5. Incompletely Specified Machines. 6. State Assignment. 7. Decomposition of Sequential Machines. 8. Exercises and Problems. 13. REALIZATION OF SEQUENTIAL NETWORKS. 1. Memory Elements. 2. Synthesis of Sequential Networks. 3. Realization of Binary Sequential Machines. 4. Realization of Synchronous Sequential Machines. 5. Pulse Mode Sequential Networks. 6. Asynchronous Sequential Networks. 7. Races and Hazards. 8. Exercises and Problems. References. Index

![[eBook Code] Spectral Logic and Its Applications for the Design of Digital Devices (eBook Code, 1st)](/img_thumb2/9780470289211.jpg)