책 이미지

책 정보

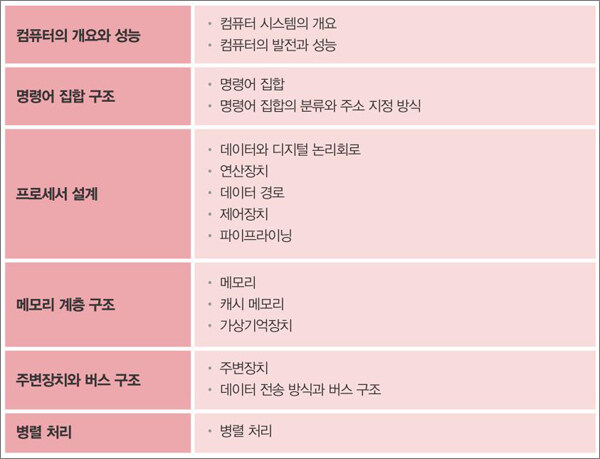

· 분류 : 국내도서 > 컴퓨터/모바일 > 컴퓨터 공학 > 컴퓨터공학/전산학 개론

· ISBN : 9791156641322

· 쪽수 : 572쪽

· 출판일 : 2014-08-08

책 소개

목차

지은이 머리말 4

이 책의 사용 설명서 6

Chapter 01 컴퓨터 시스템의 개요

1 컴퓨터 시스템 023

1 컴퓨터 시스템의 개념적 구성 023

2 컴퓨터 시스템의 4대 기능 024

3 비트, 바이트, 워드 024

2 컴퓨터 하드웨어 026

1 중앙처리장치 026

2 기억장치 027

3 주변장치 028

4 기타 하드웨어 029

3 컴퓨터 소프트웨어 032

1 시스템 소프트웨어 032

2 응용 소프트웨어 034

4 운영체제와 부팅 035

1 운영체제 035

2 부팅 035

5 컴파일러와 인터프리터 038

1 컴파일러 038

2 인터프리터 039

6 컴퓨터의 분류 041

1 처리 능력에 의한 분류 041

2 사용 목적에 의한 분류 042

3 응용 분야에 의한 분류 042

4 사용 데이터에 의한 분류 043

7 컴퓨터의 구조, 구성, 실현 044

1 컴퓨터 구조 044

2 컴퓨터 구성 045

3 컴퓨터 실현 046

4 컴퓨터 계열 046

8 하드웨어와 소프트웨어의 상호 조정 047

요약 049 연습문제 051

Chapter 02 컴퓨터의 발전과 성능

1 컴퓨터의 세대별 발전 057

2 현대 컴퓨터 발전의 지표 061

1 폰노이만 아키텍처 061

2 무어의 법칙 064

3 컴퓨터의 성능 066

1 성능의 정의 066

2 암달의 법칙 068

4 CPU 성능 분석 072

1 성능에 영향을 미치는 요소 072

2 성능에 영향을 미치는 요소의 분석 076

5 벤치마크와 성능 척도 079

1 벤치마크 079

2 MIPS와 MFLOPS 080

요약 083 연습문제 084

Chapter 03 명령어 집합

1 명령어 집합 089

1 명령어 집합의 의미 089

2 명령어 집합 구조 089

3 명령어 집합 설계 090

2 명령어의 특성 092

1 피연산자의 수 092

2 명령어의 길이 094

3 CPU의 기본 구성과 가상 명령어 집합 096

1 CPU의 기본 구성과 명령어의 실행 순서 096

2 가상 컴퓨터 명령어 098

3 좋은 명령어 집합 구조 104

4 연산 106

1 연산의 종류 106

2 분기 명령 107

3 프로시저의 호출과 복귀 111

5 명령어와 CPU 기억장치 115

요약 118

연습문제 120

Chapter 04 명령어 집합의 분류와 주소 지정 방식

1 피연산자의 수와 명령어 집합 125

1 누산기 컴퓨터 125

2 스택 컴퓨터 128

3 범용 레지스터 컴퓨터 132

2 명령어와 메모리 137

1 메모리 속성 137

2 메모리 정렬 139

3 엔디언 방식 140

3 주소 지정 방식 142

1 0-단계 주소 지정 방식 142

2 1-단계 주소 지정 방식 143

3 2-단계 주소 지정 방식 145

4 복잡도에 따른 명령어 집합 148

1 CISC의 탄생과 특징 148

2 RISC의 탄생 149

3 RISC의 특징 150

4 RISC와 CISC의 전망 152

5 picoMIPS 명령어 집합 구조 153

1 picoMIPS의 개요 153

2 picoMIPS의 명령어 형식과 종류 154

요약 157

연습문제 158

Chapter 05 데이터와 디지털 논리회로

1 데이터의 개요 163

1 데이터의 종류 163

2 데이터의 형식 164

3 데이터와 진법 164

2 정수 166

1 무부호 정수의 표현 166

2 유부호 정수의 표현 168

3 2의 보수 방식의 대중성 172

3 실수 174

1 실수의 개요 174

2 정규화와 잠복 비트 175

3 IEEE-754 표준 176

4 범위와 정밀도 178

4 비수치 데이터 180

1 BCD 코드 180

2 ASCII 코드 182

3 유니코드 183

5 디지털 논리회로 184

1 논리 게이트 184

2 조합 논리회로와 순차 논리회로 184

3 디코더와 인코더 186

4 멀티플렉서와 디멀티플렉서 188

5 반가산기와 전가산기 189

6 레지스터 파일 190

요약 192

연습문제 194

Chapter 06 연산장치

1 연산장치의 개요 199

1 연산장치와 레지스터 파일 199

2 산술장치와 논리장치의 통합 201

3 플래그 레지스터 202

2 정수의 덧셈 204

1 덧셈 연산 204

2 덧셈.뺄셈장치 206

3 정수의 곱셈 208

1 곱셈 연산 208

2 시프트-덧셈 방식의 곱셈 연산 209

3 Booth 알고리즘 213

4 정수의 나눗셈 217

1 나눗셈 연산 217

2 복원 알고리즘 218

3 비복원 알고리즘 221

5 부동 소수점의 연산 224

1 부동 소수점의 덧셈 224

2 부동 소수점의 곱셈과 나눗셈 225

3 가드 디지트 227

요약 229

연습문제 230

Chapter 07 데이터 경로

1 데이터 경로의 이해 235

1 데이터 경로 235

2 데이터 경로의 두 가지 방식 236

2 명령어 실행과 데이터 경로 239

1 picoMIPS의 명령어 형식 239

2 picoMIPS 명령어의 단계적 실행 240

3 데이터 경로의 기본 골격 241

3 단일 사이클 방식의 명령어 실행 244

1 명령어 인출 244

2 명령어 해독과 레지스터 읽기 245

3 명령어 종류별 실행 245

4 다중 사이클 방식의 명령어 실행 252

1 명령어 인출 252

2 명령어 해독과 레지스터 읽기 253

3 덧셈 명령어 실행 254

4 적재 명령어 실행 254

5 데이터 경로의 구체화와 성능 비교 257

1 데이터 경로의 구체화 257

2 단일 사이클 방식과 다중 사이클 방식의 성능 비교 261

요약 263

Chapter 08 제어장치

1 제어장치의 이해 269

1 제어장치 269

2 마이크로 연산과 제어 신호 270

3 PROM과 PLA 272

2 제어장치 구현 방식 275

1 제어 신호의 생성 275

2 제어장치 구현의 두 가지 방식 276

3 마이크로프로그래밍 방식의 제어장치 279

1 마이크로 명령어의 구성 요소 279

2 마이크로 명령어의 제어 280

3 마이크로 명령어의 형식 282

4 단일 사이클 방식 데이터 경로를 위한 제어장치 284

1 제어 신호의 종류 284

2 명령어 실행을 위한 마이크로 연산과 제어 신호 286

3 제어장치 구현 289

5 다중 사이클 방식 데이터 경로를 위한 제어장치 293

1 제어 신호의 종류 293

2 명령어 실행을 위한 마이크로 연산과 제어 신호 294

요약 301

연습문제 303

Chapter 09 파이프라이닝

1 파이프라이닝의 개요 307

2 순차 처리와 병행 처리 310

1 프로세서 구현 방식 310

2 파이프라이닝의 성능 311

3 picoMIPS 아키텍처와 파이프라이닝 314

1 구현 방식에 따른 picoMIPS의 성능 314

2 picoMIPS 파이프라인의 문제점 315

3 picoMIPS 파이프라이닝과 제어 신호 316

4 해저드 317

1 해저드의 의미와 종류 317

2 구조적 해저드 318

3 데이터 해저드 319

4 명령어 해저드 321

5 해저드의 영향과 해결 방법 324

1 해저드의 영향 324

2 해저드 해결 방법 326

6 인터럽트와 공격적 파이프라이닝 330

1 인터럽트 330

2 공격적 파이프라이닝 332

요약 335

연습문제 336

Chapter 10 메모리

1 메모리의 개요 341

1 CPU와 메모리 341

2 읽기.쓰기 동작 342

3 메모리 용량과 데이터 크기 344

4 메모리 접근 시간과 사이클 시간 345

5 저장장치의 특징 345

2 메모리의 종류와 구성 및 동작 347

1 DRAM과 SRAM 347

2 DRAM의 구성과 동작 348

3 DRAM의 확장 350

4 메모리 재충전 352

5 ROM 352

3 메모리의 성능 향상 354

1 광폭버스 메모리와 교차 메모리 354

2 파이프라인 메모리와 연관 메모리 359

4 DRAM 칩 구성의 개선과 성능 향상 360

1 FPM DRAM 360

2 EDO DRAM 360

3 RDRAM 361

4 SDRAM 361

5 차세대 메모리 364

5 메모리 계층 구조 366

1 지역성 원리 366

2 계층적 메모리의 의미와 특징 367

3 메모리 계층 구조의 원리와 전송 단위 368

4 설계 논점 370

요약 371

연습문제 373

Chapter 11 캐시 메모리

1 캐시 메모리의 개요 379

1 적중과 실패 379

2 캐시 메모리의 기본 구성과 동작 381

3 캐시 메모리의 전략과 설계 논점 383

2 블록 사상 384

1 블록 사상 방식의 개요 384

2 직접 사상 385

3 완전 연관 사상 390

4 집합 연관 사상 393

3 블록 교체와 블록 갱신 399

1 블록 교체 방식 399

2 블록 갱신 방식 401

4 캐시 메모리를 통한 성능 향상 403

1 캐시 실패의 유형 403

2 유효 접근 시간 404

3 캐시 메모리의 성능 개선 405

4 블록 크기, 캐시 용량, 캐시 연관도 406

5 다단계 캐시와 분할 캐시 408

요약 409

연습문제 411

Chapter 12 가상기억장치

1 가상기억장치의 개요 415

1 가상기억장치의 필요성 415

2 메모리 중첩 416

2 가상기억장치와 주소 변환 418

1 가상기억장치의 의미 418

2 가상기억장치의 종류 420

3 가상기억장치의 구성과 관리 기법 421

4 주소 변환 423

5 가상 주소 캐시 425

3 기본적인 주소 변환 기법 427

1 재배치 레지스터 방식 427

2 페이지 테이블 방식 429

3 세그먼트 테이블 방식 432

4 향상된 주소 변환 기법 435

1 역방향 페이지 테이블 방식 435

2 변환 색인 버퍼 방식 439

요약 442

연습문제 444

Chapter 13 주변장치

1 주변장치의 개요 449

1 주변장치 병목 현상 449

2 주변장치의 분류 450

3 성능 척도 450

2 하드디스크 452

1 하드디스크의 기초 452

2 하드디스크의 논리적 구조와 데이터 구성 453

3 주소 지정 방식 455

4 하드디스크의 성능 456

3 광학 디스크 458

1 광학 디스크의 기초 458

2 CD와 CD-ROM 459

3 DVD와 BD 460

4 기타 주변장치 462

1 입력장치 462

2 출력장치 464

3 기타 저장장치 466

5 RAID 469

1 RAID의 의미와 분류 469

2 RAID 0 470

3 RAID 1 471

4 RAID 2 471

5 RAID 3 472

6 RAID 4 473

7 RAID 5 473

8 RAID 6 474

6 입출력 시스템 475

1 입출력장치의 개요 475

2 IO 모듈 476

3 장치 구동기 477

7 입출력장치의 주소 지정 479

1 메모리 사상 입출력 방식 479

2 분리형 입출력 방식 480

요약 482

연습문제 484

Chapter 14 데이터 전송 방식과 버스 구조

1 데이터 전송 방식 489

1 프로그램 입출력 방식 489

2 인터럽트 구동 방식 491

3 직접 메모리 접근 방식 493

4 IO 채널 방식 495

2 인터럽트 497

1 인터럽트의 종류 497

2 인터럽트의 우선순위 498

3 인터럽트의 처리 499

3 버스의 개요 501

1 버스의 의미와 용어 501

2 버스에 의한 데이터 전송 과정 502

3 분리형 버스 트랜잭션 503

4 버스의 성능 향상 504

4 버스의 분류 505

1 시스템버스와 IO버스 505

2 전용 버스와 다중화 버스 506

3 동기식 버스와 비동기식 버스 507

5 버스 중재 510

1 버스 중재 방식의 개요 510

2 중앙 집중식 중재 방식 512

3 분산식 중재 방식 513

6 IO버스 표준 516

1 PCI 516

2 SATA 517

3 SAS 518

4 USB 518

5 IEEE 1394 519

요약 520

연습문제 522

Chapter 15 병렬 처리

1 병렬 처리의 개요 527

1 단일 프로세서의 한계 527

2 병렬 처리와 요구 조건 528

3 컴퓨터 시스템의 분류 529

2 SIMD 방식 병렬 처리 532

1 벡터 프로세서 532

2 GPU 534

3 다중 프로세서 시스템 535

1 다중 프로세서 시스템의 개요 535

2 UMA 구조와 NUMA 구조 536

3 멀티코어 538

4 다중 컴퓨터 시스템 540

1 다중 컴퓨터 시스템의 개요 540

2 클러스터 542

5 상호 연결망 구조 545

1 상호 연결망의 특징 545

2 정적 상호 연결망 546

3 동적 상호 연결망 550

요약 555

연습문제 557

참고자료 560

찾아보기 561

저자소개

리뷰

책속에서